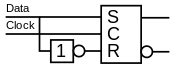

| Betrachten wir uns nun diese Schaltung:

|

|

| Nehmen wir an, dass D=0 und C=0 ist, sowie das Flipflop beim einschalten auf 0:

|

|

| Wenn wir jetzt den D Eingang auf 1 legen geschieht erstmal nicht viel:

|

|

| Erst wenn wir auch Clock auf 1 setzen, gibt das Flipflop eine 1 aus:

|

|

| Setzen wir Clock auf 0, so bleibt die 1 im Flipflop erhalten:

|

|

| Setzen wir D ebenfalls wieder auf 0, so bleibt auch hier der Ausgang auf 1, da das Flipflop ja gesperrt ist:

|

|

| Erst wenn wir Clock wieder auf 1 setzen, übernimmt das Flipflop den Zustand des Einganges wieder:

|

|

|

|

|